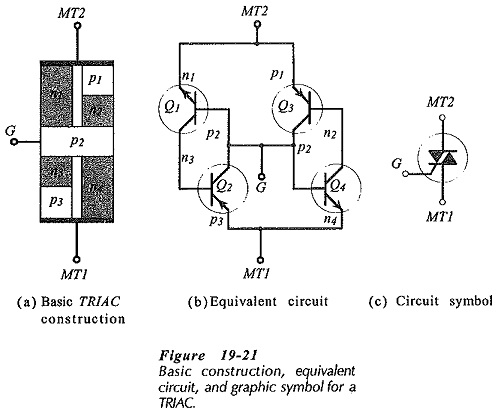

TRIAC Operation and Characteristics

TRIAC Operation and Characteristics: The basic construction, equivalent circuit, graphic symbol and TRIAC Operation and Characteristics are shown in Fig. 19-21. The TRIAC behaves as two inverse-parallel connected SCRs with a single gate terminal. Sections…