Data Types and Instruction Set of 8087 co-processor:

The Data Types and Instruction Set of 8087 co-processor can support 7 different data types namely

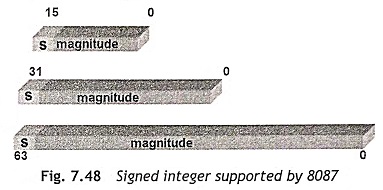

Three Signed Integers

- 16-bit (word) – range 32768 to + 32767

- 32-bit (short integer) range – 2 x 10+9 to + 2 x 10+9

- 64-bit (long integer) range -9 x 10+18 to + 9 x 10+18

A18-digit BCD data and

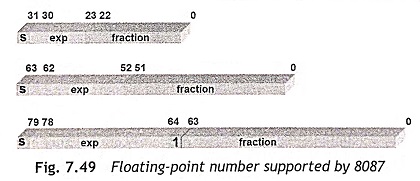

Three floating point type numbers

- 32-bit (extended precision) floating-point numbers

- 64-bit (extended precision) floating-point numbers

- 80-bit (extended precision) floating-point numbers

Figure 7.48 shows three signed integers supported by 8087

The floating-point unit hold signed integers, fractions and mixed numbers. The floating-point numbers has 3 parts such as sign bit, biased exponent and significand. The 8087 co-processor can support 3 types of floating point numbers such as

- Short (32 bits) : single precision, with a bias of 7FH

- Long (64 bits) : double precision, with a bias of 3FFH

- Temporary (80 bits) : extended precision, with a bias of 3FFFH and Fig. 7.49 shows the floating point number supported by 8087

Instruction Set of 8087

The Instruction Set of 8087 has 68 additional instructions to the instruction set of 8086. These instructions are fetched by 8086 but are executed by 8087. When the 8086 comes across an 8087 instruction, it executes the ESCAPE instruction code to bypass the instruction opcode and control of the local bus to 8087 co-processor. The execution of Instruction Set of 8087 is transparent to the programmer. The Instruction Set of 8087 are divided into six different groups as given below:

Data Transfer Instructions

- Real Transfers (Example : FLD)

- Integer Transfers (Example : FILD)

- Packed Decimal Transfers (Example : FBLD, FBSTP)

Arithmetic Instructions

- Addition (Example : FADD, FADDP)

- Subtraction (Example : FSUB, FSUBP)

- Reversed Subtraction (Example : FSUBR, FSUBRP)

- Multiplication (Example : FMUL, FMULP)

- Division (Example : FDIV, FDIVP)

- Reversed Division (Example : FDIVR, FDIVRP)

Other Arithmetic Operations (Example : FSQRT, FABS)

Compare Instructions (Example : FCOM, FCOMP, FCOMPP)

Transcendental (Trigonometric and Exponential) Instructions (Example : FPTAN, FPATAN)

Processor Control Instructions (Example : FLD)

Some of the most commonly used co-processor instructions are discussed in this section.

Floating-Point Data Transfer Instructions

FLD (Load Real) Loads 32-bit, 64-bit or 80-bit floating-point data to Top of Stack (ST). Stack pointer is then decremented by 1. Data can be retrieved from memory, or another stack register. The examples of FLD instructions are as follows:

- FLD ST(2); Top of stack ← [ST(2)]; Copies the contents of register ST(2) to top of the stack.

- FLD Memory_32; Top of stack ← [Memory_32]; Copies the contents of memory_32 to top of the stack.

FST (Store Real) This instruction stores the content of the top of the stack into memory or a specified co-processor register. During copy, the data rounding occurs using the rounding control bits in floating point control of register. The examples of FST instructions are as follows:

- FST ST(1); [ST(1)] ← Top of stack; Copies the contents of top of the stack to register ST(1).

- FST Memory_64; [Memory_64] ← Top of stack; Copies the contents of top of the stack to memory_64.

FSTP (Store Floating Point Number and Pop) This instruction stores a copy of the top of the stack into memory or any specified co-processor register and pop the data from the top of stack. The examples of FSTP instructions are as follows

- FSTP ST(4); [ST(4)] ← Top of stack, Copies the contents of top of the stack to register ST(4).

- FST Memory_32; [Memory_32] ← Top of stack; Copies the contents of top of the stack to memory_32.

FXCH (Exchange) The FXCH instruction exchanges the contents of specified register with top of stack. The example of FXCH instruction is

- FXCH ST(2); [ST(2)] <–> Top of stack; Exchanges the contents of top of the stack with register ST(2).

Integer Data-Transfer Instructions During transferring the data, the co-processor automatically converts extended floating-point number to integer data. There are three types integer data transfer instructions such as

- FILD (Load integer)

- FIST (Store integer)

- FISTP (Store integer and pop)

For example,

- FILD ST(3); Top of stack ← [ST(3)]; Copies the contents of register ST(3) to top of the stack.

- FILD Memory; Top of stack ← [Memory]; Copies the contents of memory to top of the stack.

The instructions FIST and FISTP work in an exactly similar manner as FST/FSTP except that the operands are integer operands.

For example,

- FIST ST(5); ST(5) ← Top of stack; Copies the contents of top of the stack to register ST(5).

- FST Memory_64; [Memory_64] ← Top of stack; Copies the contents of top of the stack to memory_64.

BCD Data-Transfer Instructions The 8087 has two BCD data transfer instructions such as

- FBLD (loads the top of stack with BCD memory data), and

- FBSTP (stores top of the stack and does a pop).

Both the instructions work in an exactly similar manner as FLD and FSTP except that the operands are BCD numbers.

Arithmetic Instructions The 8087 co-processor has 11 arithmetic instructions that can be used to perform arithmetic operations such as addition, subtraction, multiplication and division or supporting operations like scaling, rounding, negation, absolute value, etc. Some arithmetic instructions are explained below:

FADD and FADDP These two instructions perform real or integer addition of the specified operand with the stack top. After addition, the results are stored in the destination operand. The operand may be any of the stack registers or a memory location. For example,

- FADD ST(0), ST(1); ST(0) ← ST(0) + ST(1) , destination = destination + source.

- FADDP ST(3), ST(0); ST(3) ← ST(3) + ST(0) , destination = destination + source.

FSUB, FSUBP, FSUBR and FSUBRP These four instructions perform real or integer subtraction of the specified operand from the stack top. The operand may be any of the stack register or memory. After subtraction, the result of the operation is stored in the destination operand. For example,

- FSUB ST(0), ST(1); ST(0) ← ST(1)+ST(0), destination = destination-source.

- FSUBP ST(3), ST(0); ST(3) ← ST(0)+ST(3), destination = destination-source.

The FSUBR and FSUBRP instructions work in a similar manner but these instruction perform reverse subtraction such as destination = source-destination. For example,

- FSUBR ST(0), ST(1); ST(0) ← ST(1)-ST(0) , destination = source-destination.

- FSUBRP ST(3), ST(0) ; ST(3) ← ST(0)-ST(3) , destination = source-destination.

FMUL and FMULP These two instructions perform real or integer multiplication of the specified operand with stack top. The specified operand may be a register or a memory location. After multiplication, the result will be stored in the destination operand. For example,

- FMUL ST(0), ST(1); ST(0) ← ST(0) x ST(1) , destination = destination x source.

- FMULP ST(3), ST(0); ST(3) ← ST(3) x ST(0) , destination = destination x source.

FDIV, FDIVP, FDIVR and FDIVRP These four instructions perform real or integer division. When the destination is not specified, the top of stack is the destination operand and source operand may be a memory operand of short real or long real type. If both destination and source operands are specified then compute the division and store the result in the destination. For example,

- FDIV ST(0), ST(1); ST(0) ← ST(0) / ST(1) , destination = destination / source.

- FDIVP ST(3), ST(0); ST(3) ← ST(3) / ST(0) , destination = destination / source.

The FDIVR and FDIVRP instructions work in similar way but these instructions perform reverse division such as destination = source/destination. For example,

- FDIVR ST(0), ST(1); ST(0) ← ST(1) / ST(0) , destination = source / destination,

- FDIVRP ST(3), ST(0); ST(3) ← ST(0) / ST(3) , destination = source / destination.

FSQRT The FSQRT instruction finds out the square root of the content of the top of stack and stores the result on the stack top. The value of the top of stack must he zero or positive otherwise FSQRT generates an invalid exception.

FABS The FABS instruction computes the absolute value of the content of the stack top and the result is stored in the top of stack.

The following letters are used to additionally qualify the arithmetic operations:

- P – Perform a register pop after the operation.

- R – Reverse mode for subtraction and division.

- I – Indicates that the memory operand is an integer. ‘I’ appears as the second letter in the instruction, such as FIADD, FISUB, FIMUL, FIDIV.

Comparison Instruction The comparison instructions of the 8087 co-processor are FCOM, FCOMP, FCOMPP, FUCOM, FUCOMP, and FUCOMPP which are used to compare the two values on the top of stack and set the condition code flags appropriately. The example of comparison instruction is

- FCOM ST(1); compare ST(0) against ST(1) and set the processor accordingly

Transcendental Instructions The 8087 co-processor has eight transcendental operation instructions such as FTAN, FPTAN, F2XMI, FLY2X, FLY2XP1, FSIN, FCOS and FSINCOS. In this section only FTAN, FPTAN, FLY2X, and FLY2XP1 are explained.

FPTAN The FPTAN instruction is used to compute the partial tangent of an angle θ, where θ must be in the range θ° ≤ θ ≤ 90°. The value of angle must be stored at the stack top. The result is computed in the form of a ratio of ST/ST(1).

FPATAN The FPATAN instruction calculates the are tangent (inverse tangent) of a ratio ST(1)/ST(0). The stack is popped and the result is stored on the top of stack. Its function can be expressed as

FYL2X This instruction is used to calculate log2 X where X must be in the range of 0 ≤ X ≤ ∞ and Y must be in the range 0 ≤ Y ≤ ∞.

FYL2XP1 This instruction is used to compute the function log2 (X + Y). This instruction is almost identical to FYL2X except that it gives more accurate results when computation log of a number very close to one.

Co-processor Control Instructions The co-processor control instructions are used to program the numeric processor or to handle the internal functions like flags manipulations, exception handling, processor environment maintenance and preparation, etc. The 8087 coprocessor control instructions are FINIT, FENI, FDISI, FLDCW, FSTCW, FSTSW, FCLEX, FINCSTP, FDECSTP, FFREE, FNOP, FWAIT, FSTENV, FLDENV, FRSTOR and FSAVE. In this section, operation of FINIT, FENI, FDISI and FWAIT instructions are discussed.

FINIT The FINIT instruction initializes the 8087 for further execution. In other words, this instruction must be execute and the hardware will be reset before executing FPU instructions. The instruction initializes the control word register to 03FFH, the status register to 0 and the TAG status is set empty. All the flags are cleared and the stack top is initialized at ST (0).

FENI The FENI instruction enables the interrupt structure and response mechanism of 8087. Therefore, the interrupt mask flag is cleared.

FDISI The FDISI instruction sets the interrupt mask flag to disable the interrupt response mechanism of 8087.

FWAIT The FWAT instruction is used by the 8087 co-processor causes the microprocessor to wait for the coprocessor to finish an operation.