Demultiplexing of Address and Data Bus in 8086 and 8088 Microprocessors:

Demultiplexing of Address and Data Bus in 8086 and 8088 Microprocessors which consists of three buses: address, data and control buses. The address/data buses are operated in time-multiplexed mode. The address bus is required to locate memory and I/O devices for data transfer through memory and I/O read or write cycles. The data bus is used to transfer data from microprocessor to memory/I/O devices or vice versa. The control bus provides control signals to memory/I/O devices for data-transfer operations.

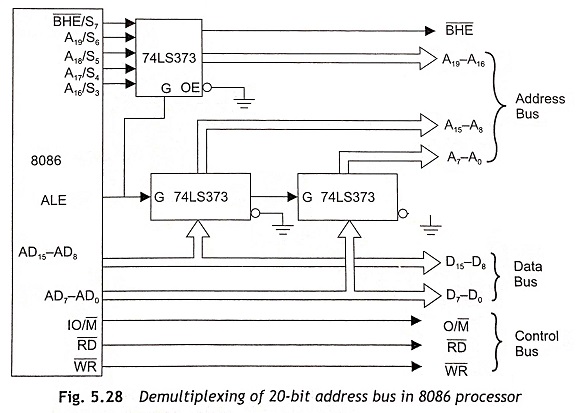

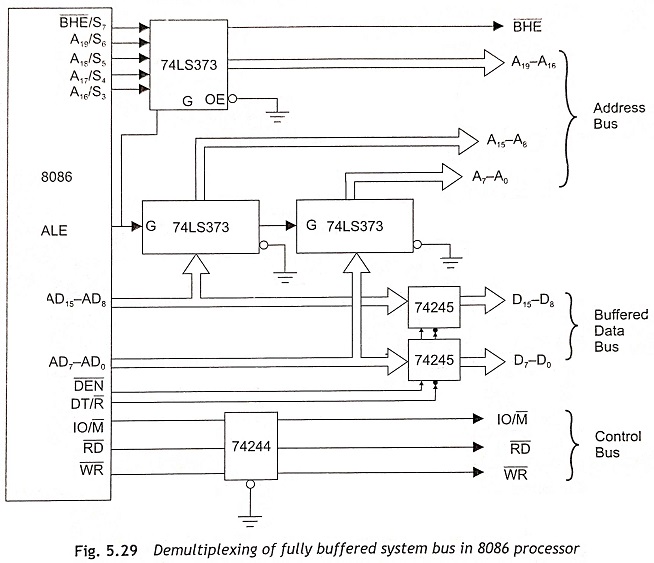

Demultiplexing of System Bus in 8086 processor

The 8086 microprocessor has time-multiplexed 16-bit address/data bus AD15-AD0 and 4-bit address/status bus A19/S6-A16/S3. The ALE signal is used to latch the address of 8086. Usually, latch ICs are available with eight separate latches. Therefore, three latch ICs should be used for demultiplexing 20-bit address lines. Figure 5.28 shows the circuit diagram for latching 20-bit address lines using three 74LS373 latch ICs. In this arrangement, two ICs are fully utilized and one latch is partially used.

The 8086 microprocessor has 16-bit time-multiplexed data bus which is available as Address/Data bus, AD15-AD0.The data bus is always separated from the address bus by using 74245 buffers as depicted in Fig. 5.29. The data bus is bi-directional and data can he transferred from microprocessor to memory and memory to microprocessor for memory write and read operations respectively. The control signals D̅E̅N̅ and DT/R̅ represent the presence of data on the data bus and directional flow of data. These signals are used to connect the chip enable CE and directional pins of 74245 buffers. While D̅E̅N̅ is low, the data is available on the multiplexed bus.

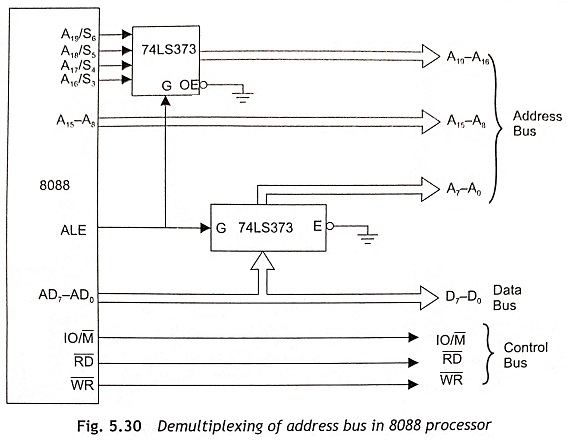

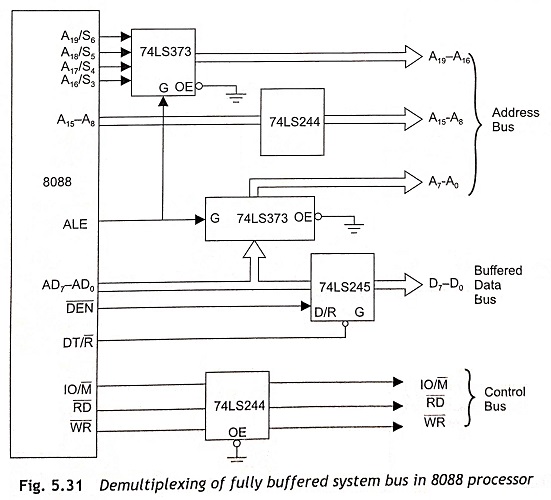

Demultiplexing Of System Bus in 8088 processor

In 8086 A19/S6-A16/S3, AD15-AD0 and B̅H̅E̅/S7 are multiplexed but in 8088 only A7-A0 and A19/S6-A16/S3 are time multiplexed. The demultiplexing of address bus of the 8088 microprocessor is shown in Fig. 5.30. Here, 74LS373 latches are used to demultiplex address/data bus. When ALE = 1, the latches pass the inputs to the outputs. After one clock time T1, ALE becomes logic 0. A19/S6-A16/S3 are connected into the top latch and A7-A0 are connected into the bottom latch. These address connections can are able to address 1 MB memory space. The 8088 systems require only one data buffer due to the 8-bit data bus as depicted in Fig. 5.31.