IC Packaging Process | IC Package Types:

After completing all the fabrication processes, several chips are ready on a wafer. Each of the chip is nothing but a complete circuit. Now the next step is to separate out these chips and package them individually. Using a diamond tipped tool lines are scribed along the rectangular grides on the surface of the wafer. The wafer is cut off along the lines drawn using the sharp diamond tipped tool. Thus individual chips are separated from each other. Then each chip is assembled on a suitable package. This process is called IC Packaging.

For comparing and assessing different integrated circuit package types, following features are considered

- Maximum pin count.

- Dimensions

- Pitch (spacing between the centres of adjacent pins)

- Encapsulating material (ceramic or plastic)

- Mode of mounting (plated through hole-TH or surface mount – SM)

- Maximum power dissipation

IC Package Types:

For TH mounting DIP (dual in line package) and PGA (pin grid array) are the only standard packages. For small scale integration (SSI) and medium scale integration (MSI), the different IC Packaging Process available are SIP (single in-line package), ZIP (zig-zag-in-line package) and QIPC, quad-in-line package with TH mounting type. For low pin counts the packages available are SO (small out line package), SSOP (Shrunk small out line package). Both these are with SM mounting type.

With SM mounting types, there are two more IC Packaging Process, namely chip carrier and TQFP (thin quad flat pack). The chip carrier uses either plastic or ceramic as encapsulating material. The TQFP has very low profile and small weight.

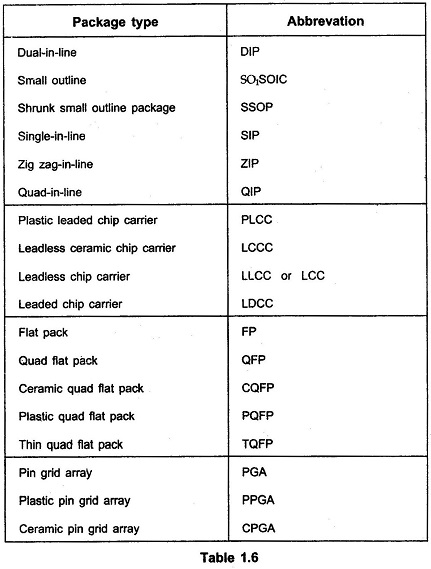

Table 1.6 gives the IC Package Types with their abbreviations.

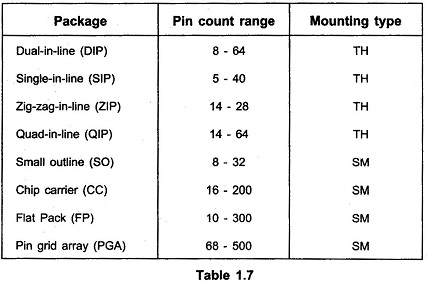

Table 1.7 summarizes typical IC Packaging with typical pin counts and mounting type.