Interrupt Priority in 8086:

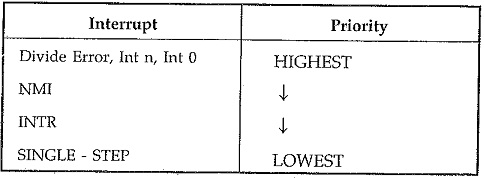

As far as the Interrupt Priority in 8086 are concerned, software interrupts (All interrupts except single step, NMI and INTR interrupts) have the highest priority, followed by NMI followed by INTR. Single step has the least priority.

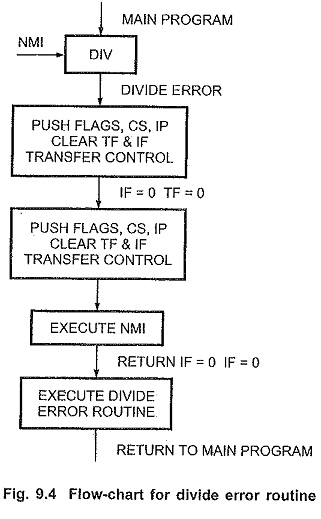

The interrupt flag is automatically cleared as part of the response of an 8086 to an interrupt. This prevents a signal on the INTR input from interrupting a higher priority interrupt service routine. The 8086 allows NMI input to interrupt higher priority interrupt, for example suppose that a rising edge signal arrives at the NMI input while the 8086 is executing a DIV instruction, and that the division operation produces a divide error. Since the 8086 checks for internal interrupts before it checks for an NMI interrupt, the 8086 will push the flags on the stack, clear TF and IF, push the return address on the stack, and go to the start of the divide error service routine.

The 8086 will then do an NMI interrupt response and execute non-maskable interrupt service routine. After completion of NMI service routine an 8086 will return to the divide error routine. It will execute divide error routine and then it will return to the main program (refer Fig. 9.4).

Interrupt Acknowledge Cycle:

In the minimum mode, the M/IO is low indicating I/O operation during the INTA bus cycles. The 8086 activates LOCK signal by making it low from T2 of the first cycle until T2 of the second bus cycle to avoid the BIU from accepting a hold request between the two INTA cycles.

In the maximum mode, the statics lines S0 to S2 enable the INTA output for each cycle via the 8288. The 8086 activates LOCK froth T2 of the first cycle until T2 of the second to prevent the 8086 from accepting a hold request on either RQ/GT inputs and to prevent bus arbitration logic from releasing the bus between INTAs in multiprocessor system.