JFET as an Amplifier:

One of the applications of JFET as an Amplifier of input signal.

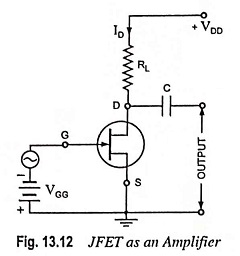

In FET the weak signal is applied between gate and source and an amplified output is taken across the drain-source circuit having load, as shown in Fig. 13.12, just as in a vacuum tube where signal is connected between grid and cathode and output is taken across a load connected in plate circuit.

For proper working of JFET it is necessary that the gate is made negative w.r.t. source (i.e. the input circuit is always reverse biased). This is achieved either by inserting a battery VGG in the gate circuit with the polarity shown in Fig. 13.12 or by providing a biasing circuit.

On application of an alternating weak signal, the fixed reverse bias of the gate changes and a small change in reverse bias on the gate causes a large change in drain current owing to change in width of the channel. This fact makes the FET capable of amplifying the strength of weak signals. During the positive half cycle of the input signal, the reverse bias on the gate decreases causing increase in channel width and hence the drain current.

During the negative half cycle of the input signal, the reverse bias on the gate increases causing drain current to decrease. The result is that the small change in voltage at the gate produces a large change in the drain current. These large variations in drain current provide large output across the load RL and thus, JFET as an Amplifier.