Operating Modes of 8257:

The Operating Modes of 8257 can be programmed to operate in following modes :

Rotating Priority Mode :

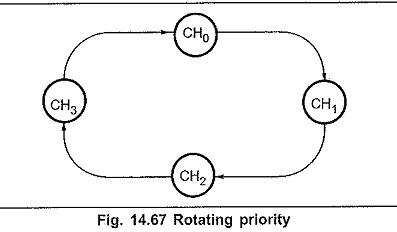

In rotating priority mode, the priority of the channels has a circular sequence. In this, channel being serviced gets the lowest priority and the channel next to it gets the highest priority as shown in Fig. 14.67.

Thus, with rotating priority in a single chip DMA system, any device requesting service is guaranteed to be recognized after no more than Jhree higher priority services have occurred. This prevents any one channel from monopolizing the system. The rotating priority mode can be set by writing logic ‘1’ in the bit 4 of the mode set register.

Fixed Priority Mode :

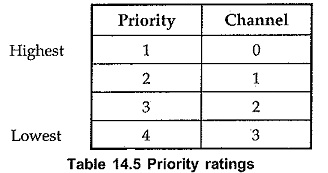

In the fixed priority, channel 0 has the highest priority and channel 3 has the lowest priority. Table 14.5 shows the priority ratings.

In the fixed priority, after recognition of any one channel for service, the other channels are prevented from interfering with that service until it is completed. If bit 4 of mode set register is logic 0, Operating Modes of 8257 operates in fixed priority mode.

Extended Write Mode :

Microcomputer systems allow use of various types of memory and I/O devices with different access time. If a device can not be accessed within a specific amount of time it returns a “not ready” indication to the 8257 that causes the 8257 to insert one or more wait states in its internal sequencing. The extended write option provides alternative timing for the I/O and memory write signals which allows the devices to return an early READY and prevents the unnecessary occurrence of wait states in the Operating Modes of 8257. It does this by activating MEMW and IOW signals earlier in the DMA cycle, giving more setup time.

TC STOP Mode :

If the TC stop bit is set, a channel is disabled (i.e. its enable bit is reset) after the terminal count (TC) output goes high, thus automatically preventing further DMA operation on that channel. To enable DMA operation on the channel it is necessary to set enable bit of the corresponding channel in the mode set register. If the TC STOP bit is not set, the occurrence of the TC output has no effect on the channel enable bits.

Auto Load Mode :

Auto load Mode when enabled, permits block chaining operations, without immediate software intervention between blocks. In this mode, channel 2 parameters (DMA starting address, terminal count and DMA transfer mode) are initialized as usual for the first data block. These parameters are automatically duplicated in the channel 3 registers when channel 2 is initialized. After the first block of DMA cycles is executed by channel 2 (i.e., after the TC output goes high), the parameters stored in the channel 3 registers are transferred to channel 2 during an ‘update’ cycle and next block of DMA cycle is executed. This repeat block operations can be used in applications such as CRT refreshing.

During the update cycle, it is necessary to prevent the CPU from inadvertently skipping a data block by overwriting a starting address or terminal count in the channel 3 registers before those parameters are properly auto-loaded into channel 2.

DMA Cycles:

DMA READ : In this cycle, data is transferred from memory to I/O device.

DMA Write : In this cycle, data is transferred from I/O device to memory.

DMA Verify : In this cycle, data is not transferred between memory and I/O It is used by the, peripheral device to verify the data that has been recently transferred. To avoid overwriting registers of channel 3, update flag in the status register can be monitored by the CPU.

Note : 1. In the auto load mode, channel 3 is still available to the user if the channel 3 enable bit is set, but use of this channel will change the values to be auto loaded into channel 2 at update time. 2. In the auto load mode, TC stop feature has no effect on channel 2.