Operating Modes of 8279:

The Operating Modes of 8279 provides 3 basic input modes :

-

Scanned keyboard

-

Scanned sensor matrix

-

Strobed input

Scanned Keyboard:

In this mode, keyboard can be scaned in two ways : Encoded scan and decoded scan.

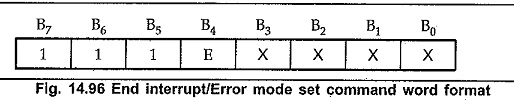

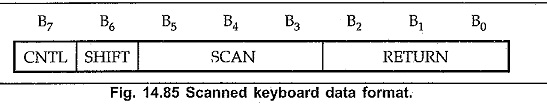

Encoded scan : In the encoded scan, scan lines (SL2-SL0) are decoded externally to provide 8 scan lines. We know that Operating Modes of 8279 provides 8 returns lines. Therefore, the maximum size of keyboard matrix is 8 x 8 = 64. When the key is pressed, 8279 stores the encoded status of scan lines and return lines along with the status of SHIFT and CNTL/STB keys into the FIFO RAM, as shown in the Fig. 14.85.

CNTL is the MSB of the character and shift is the next most significant bit. The next three bits are from the scan counter. The last three bits indicate to which return line the key is connected. With this 8-bit key code Operating Modes of 8279 can recognize 256 (28) different characters.

CNTL is the MSB of the character and shift is the next most significant bit. The next three bits are from the scan counter. The last three bits indicate to which return line the key is connected. With this 8-bit key code Operating Modes of 8279 can recognize 256 (28) different characters.

Display Modes:

The Operating Modes of 8279 provides 2 basic output modes

-

Left Entry (type writer type)

-

Right Entry (calculator type) Left Entry

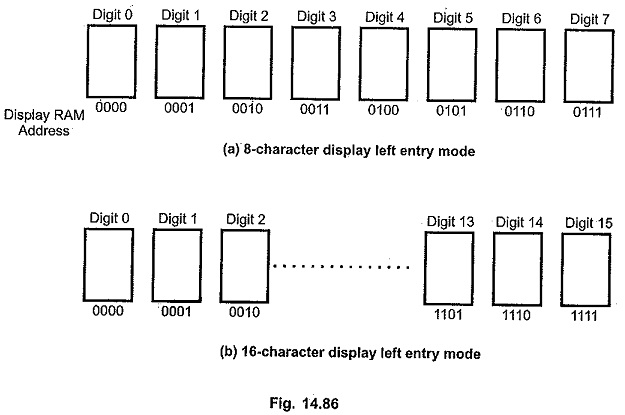

In the left entry mode, Operating Modes of 8279 displays characters from left to right in the multiplexed displays like a typewriter. In this, each display position is directly corresponds to a byte (or nibble) in the display RAM. Address 0 in the RAM is the left-most display character and address 15 (or address 7 in 8 character display) is the right most display character, as shown in the Fig. 14.86 (a) and (b).

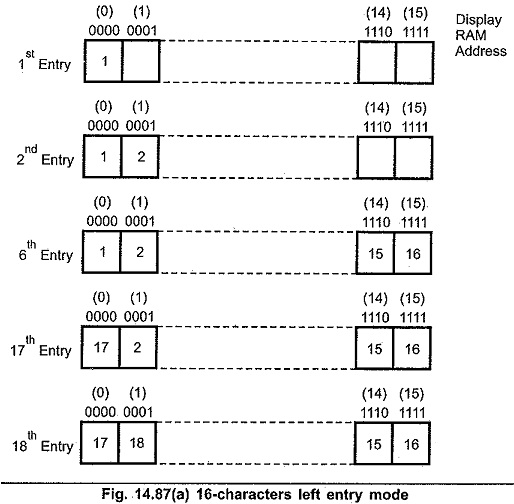

Entering characters from possible zero causes the display to fill from the left. The 17th (9th in case 8 character display) character is entered back in the left most position and filling again proceeds from there, as shown in the Fig. 14.87 (a). The characters can be displayed on the specific digit by loading character code in the corresponding location in the display RAM

Autoincrement in Left Entry:

In left entry mode, if autoincrement flag is set to 1 after each write operation display RAM address is incremented by one so that it will point the next location in the display RAM. This autoincrement facility allows user to load display RAM in a sequential manner, and it is not necessary to specify display RAM address for each write operation.

Right Entry:

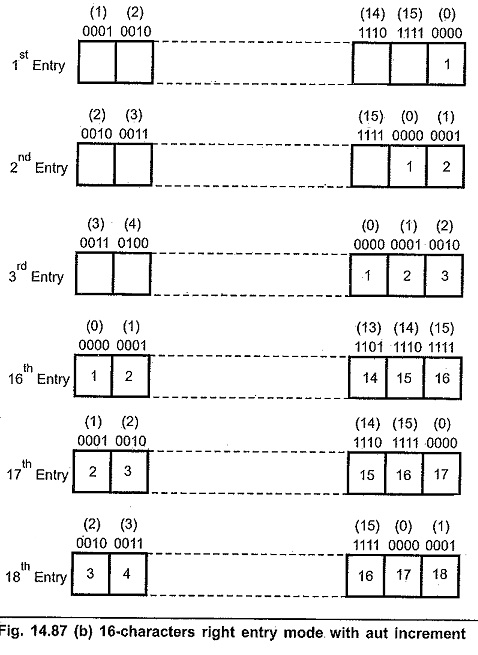

In the right entry mode, Operating Modes of 8279 displays characters from right to left in the multiplexed display like a calculator. The first entry is displayed on the right most display. The next entry is also displayed on the right most display after the display is shifted left one character, as shown in the Fig. 14.87 (b).

When new character is entered, it shifts all previous characters left by one position and displays new entry on the right most display.

Autoincrement in Right Entry:

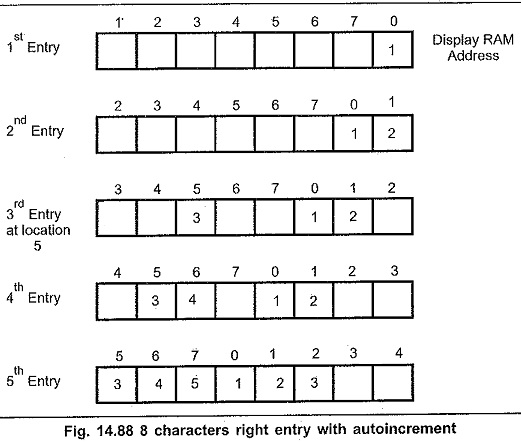

In the right entry mode, auto incrementing and non autoincrementing have the same effect as in the left entry except if the address sequence is changed. Some examples with changed address sequence

First character is displayed on the right most digit of the display. After second entry first character is shifted left and second character is displayed on the right most digit of the display. In the third entry, address of display RAM is changed to 5, displaying the third character at fifth digit after shifting the previous characters 1 digit left. In the 4th Entry the new character is displayed at 5th digit after shifting all previous characters 1 digit left, and this sequence is continued (Fig. 14.88).

8279 Commands:

In the last sections we have seen various operating modes of Operating Modes of 8279. To program 8279 in the desired mode it provides eight command words. The command words are sent on the data bus with CS low and A0 high and are loaded to the 8279 on the rising edge of WR. 8279 differentiate these commands by checking 3 most significant bits of the command word.

Keyboard/Display Mode Set Command (000):

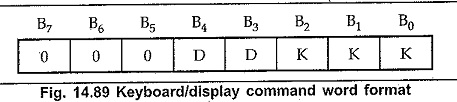

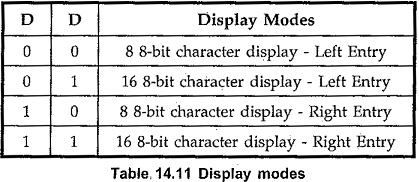

This command is used to program operating modes of keyboard and display. Three least significant bits decide the keyboard mode and next two bits decide the display mode, as shown in the tables.

Command Word Format:

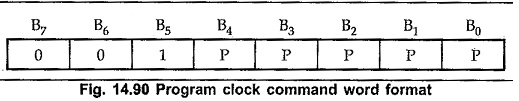

Program Clock Command (001):

All timing and multiplexing signals for the Operating Modes of 8279 are generated by an internal prescaler. This prescaler divides the external clock by a programmable integer value given in the program clock command word, to generate internal frequency Fig. 14.90 shows format for program clock command word.

Bits PPPPP determine the value of this integer which ranges from 2 to 31. To give proper scan and key debounce times the internal frequency should be 100 kHz. Therefore, prescaler integer value should be selected to get 100 kHz internal frequency.

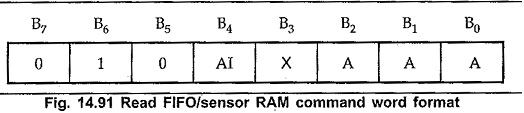

Read FIFO/Sensor RAM Command (010):

To read data from FIFO/sensor RAM, it is necessary to set 8279 in read FIFO/sensor RAM mode. Read FIFO/sensor RAM command is used for this purpose Fig. 14.91 shows the format for Read FIFO/Sensor RAM command.

Here, three least significant bits, (AAA) specify the address of the sensor RAM and bit B4, if 1 enables autoincrement mode. In the scan keyboard mode, the autoincrement flag (AI) and the FIFO RAM address bits (AAA) are irrelevant. In this mode, Operating Modes of 8279 provides data for each subsequent read in the same sequence in which the data first entered in the FIFO RAM.

In the sensor matrix mode, the sensor RAM address bits AAA select one of the 8 rows of the sensor RAM. If the autoincrement flag is set (AI = 1), each successive read will be from the subsequent row of the sensor RAM.

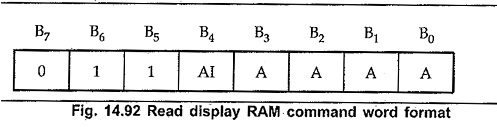

Read Display RAM Command (011):

To read data from display RAM, it is necessary to set 8279 in read display RAM mode. Read display RAM command is used for this purpose. Fig. 14.92 shows the format for Read Display RAM command

Here, four least significant bits (AAAA) Specify the address ‘of the 16 byte display RAM and bit B4, if 1, enables autoincrement mode. If the bit B4 (AI) is set, display RAM address is incremented after each read command to display RAM.

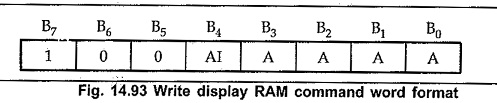

Write Display RAM Command (100):

To write data into display RAM, it is necessary to set 8279 in write display RAM mode. Write display RAM command is used for this purpose. Fig. 14.93 shows the format for write Display RAM command.

Here, four least significant bits (AAAA) specify the address of the 16 byte display RAM and bit B4, if 1, enables autoincrement mode. If the bit B4 (AI) is set, display RAM address is incremented after each write command to display RAM.

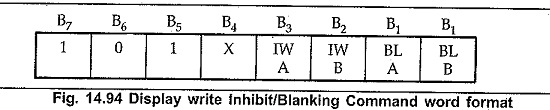

Display Write Inhibit/Blanking Command (101):

We know that, display RAM data is sent on the two 4-bit ports (B3 — B0 and A3 —A0) This two 4-bit pots can be individually inhibited or blanked with display write inhibit/blanking command. Fig. 14.94 shows the format for display write Inhibit/Blanking Command

The IW bits are used to mask nibble A (4-bit port A) and nibble B (4-bit port B) in applications requiring separate 4-bit display ports. By setting the IW flag (I/W = 1) for one of the ports, the port can be masked so that entries to the display RAM from the CPU do not affect other port.

The BL bits are used to blank the individual nibbles. This command loads the blank code (All zeros, 20H, or All ones) determined by the last issued clear command, in the display RAM to blank the display.

Note : After reset blank code is set to all zeros.

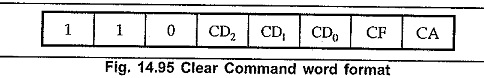

Clear Command (110):

Clear command is used to clear all the rows of the display RAM with a selectable blanking code, to clear status of FIFO RAM and to reset interrupt output line. Fig. 14.95 shows the format of display command

CD bits (CD0 — CD1 ) are used to select the blanking code as given below

Bit CD2, when set to one, enables clear display

Bit CF, when set to one, clears the status of the FIFO, resets the interrupt output line and sets the sensor RAM address to 000.

CA, the clear all bit, has the combined effect of CD and CF; it uses the CD clearing code on the displays RAM and also clears FIFO status. It also resynchronizes the internal timing chain.

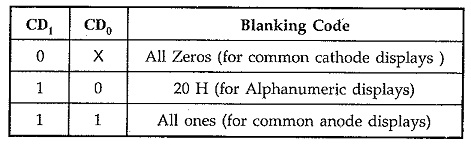

End Interrupt/Error Mode Set Command (111):

In the sensor matrix mode, if any change in sensor value is detected, IRQ line goes high at the end of a sensor matrix scan. The IRQ line is cleared by the first data read operation if the autoincrement flag is set to zero. But if autoincrement flag is set to one then it is necessary to issue End Interrupt Command to clear the IRQ line. Fig. 14.96 shows the format for End Interrupt/Error mode set command.

For the N key rollover mode, if the E bit is programmed to ‘1’, the 8279 will operate in the Special Error Mode. In the special error mode, if two keys are depressed during single debounce, the error flag in the FIFO status word is set.