Registers of 80386 Microprocessor:

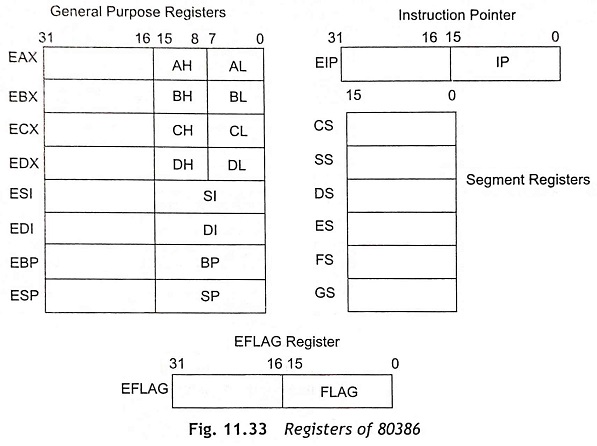

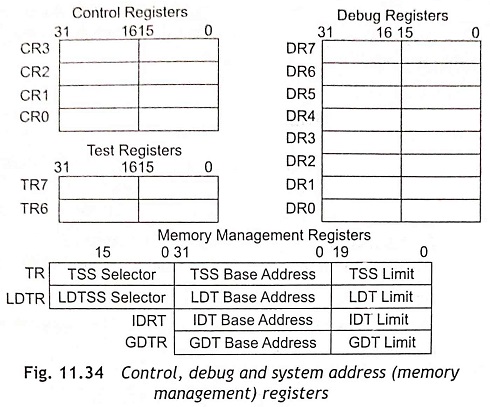

The 80386 processor has significantly extended the 8086 register set. All the registers of 80286 are existing in the 80386 processor and some new registers have been added in 80386. Generally, the registers of 80386 microprocessor are of 32 bits and they can be used as 8-bit and 16-bit registers. Figure 11.33 and Table 11.19 show the Registers of 80386 Microprocessor.

The registers of 80386 are divided as general-purpose registers and special registers.

General-purpose registers are

- 32-bit EAX, EBX, ECX, EDX, ESI, SDI, EBP and ESP.

Special registers are

- Segment (selector) registers 16-bit CS, DS, ES, SS, FS, and GS

- 32-BIT EIP

- EFLAGs

32-BIT EIP The IP of 8086 and 80286 can only support program segments of 64 KB but the EIP register is able to support programs up to 4 GB. The CS register enables larger programs and its content can be changed under program control. The instruction pointer cannot be written directly by the program. The IP can be changed by execution of JUMP, CALL, RETURN and INTERRUPT instructions. For example, during execution of FAR CALL and JUMP instructions, the values of CS as well as IP are changed to locate a new physical memory location.

Stack Segment and Stack Pointer Each program has a stack segment. In the 8086 microprocessor, the stack grows downward and the value of the stack pointer decreases with execution of PUSH instruction and increases with execution of POP instruction. In the 80386 processor, when the data is stored on the stack, the value of ESP is decreased by 4 as the 80386 always writes a complete double word or 4 bytes. If the 80386 operates in 16-bit mode, two bytes will be stored on the stack and the value of SP will be reduced by 2 after each PUSH command.

General-Purpose Registers The general-purpose registers is able to hold 8-, 16-, or 32-bit data. The 8086 microprocessor has byte and word-sized registers, but the 80386 contains double-word sized or extended registers. The 8- and 16-bit registers can be addressed just like the 8086 processor.

The AX, BX, CX, DX, SI, DI, BP, SP, FLAGS and IP registers are 16-bit registers and they have been extended to 32 bits. A 32-bit register is called an extended register and it is represented by the register name with prefix E. For example, a 32-bit register corresponding to AX is represented by EAX. Similarly, all 32-bit general-purpose registers are represented by EAX, EBX, ECX, EDX, ESI, EDI. The other 32-bit registers are EBP, ESP, EFLAGS, and EIP.

Segment Registers Besides the above 32-bit registers, the 80386 also provides 2 new 16-bit segment registers such as FS and GS. Therefore, all segment registers of 80386 are CS, DS, ES, SS, FS, and GS. The FS and GS registers are additional extra segment registers which allows access 6-different segments in memory without reloading a segment register. In real-mode operation, segment registers contain a segment address and in protected mode operation, they contain a selector just as in the 8086.

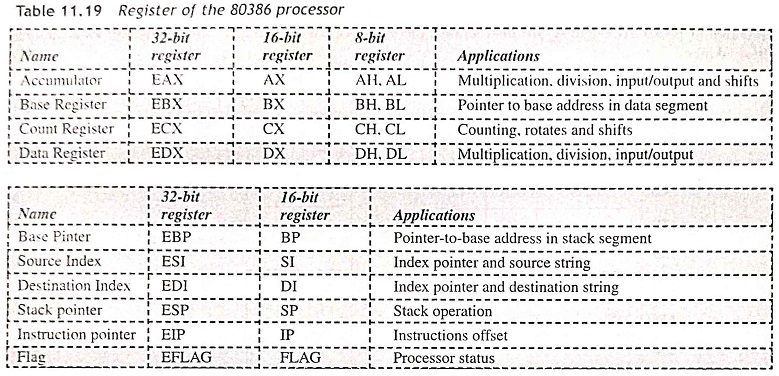

Control Registers The 80386 processor has four 32-bit control registers: CR0-CR3. These registers are used to hold global machine status. The load and store instructions are used to access these registers. In 80386, these registers perform paged memory management, cache enable/disable and protected mode operation. Figure 11.34 shows the control registers.

Debugging Registers The 80386 has eight 32-bit debug registers DR7-DR0 for hardware debugging as depicted in Fig. 11.34. Among the eight debugging registers, two registers DR5 and DR4 are reserved by Intel. The first four registers DR3 to DR0 are used to store four program controllable breakpoint addresses. The DR7 and DR6 hold breakpoint control and breakpoint status information respectively.

Test Registers Two test registers TR6 and TR7 exist in the 80386 processor for page caching as shown in Fig. 11.34. TR6 is known as test control and TR7 is called a test status register.

System Address Registers The 80386 has four system address registers to refer the descriptor tables as shown in Fig. 11.34. The four different types of descriptor tables are Global Descriptor Table (GDT), Interrupt Descriptor Table (IDT), Local Descriptor Table(LDT), Task State Segment descriptor (TSS).

The system address and segment registers are used to hold the addresses of descriptor tables GDT, IDT, LDT and TSS and their respective segments. These registers are called GDTR, IDTR, LDTR and TR respectively. The GDTR and IDTR are known as system address, but the LDTR and TR are known as system segment registers.

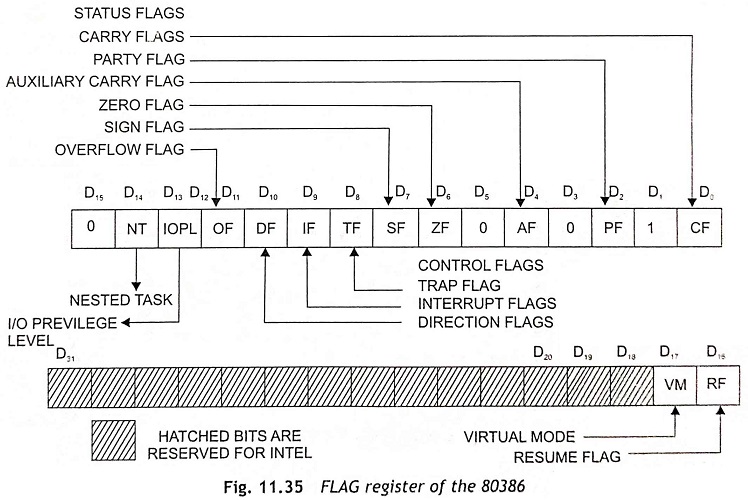

FLAG Register The flag register of the 80386 is a 32-bit register as shown in Fig. 11.35. Among these 32 bits, D31 to D18, D15, D5 and D3 are reserved by Intel and D1 is always 1. The lower fifteen bits of flag register of 80386 are same as 80286. Only two flags are newly added to the 80286 flag register to get the flag register of 80386. The two new flags are VM and RF flags.

RF (Resume Flag) This is the first bit in the extended EFLAGS register. It is used with the debug register breakpoints. At the starting of each instruction cycle, the status of RF is always checked. If RF = 1, any debug fault will be ignored while executing any instruction. This flag is automatically reset after execution of instructions except IRET and POPE.

VM (Virtual Mode Flag) When this flag is set, the 80386 enters in the virtual 8086 mode within the protected mode. If VF is set, 80386 operates in protected mode. When this flag is cleared or reset, the 80386 operates in real address mode.