Virtual 8086 Mode in Microprocessor:

The virtual 8086 mode is a special operating mode of the Pentium processor and it is a subset of protected mode. In this mode, two 8086 application programs can be executed at the same time. During virtual 8086 mode operation, the segment registers are used in the similar way as in real mode. Consequently, the segment and an offset address are used to address 1 Mbyte memory locations starting from 00000H to FFFFFH. After incorporating paging, any program can use addresses below 1 Mbyte memory space, but the Pentium processor is able to use any address in the 4 Gbyte physical memory. When the VM bit of the EFLAG register is 1 or VM = 1, the processor becomes enabled to operate in virtual 8086 mode.

The paging technique supports ‘virtual memory’ and a large linear address space is simulated with a small amount of physical memory such as RAM and ROM and disk storage. With the application of paging, each segment is divided into pages. Usually each page size is 4 Kbytes, which are stored either in physical memory or on the disk.

The operating system always maintains a page directory and a set of page tables to keep track of the pages.

Whenever a program tries to access an address location in the linear address space, the Pentium processors use the page directory and page tables to convert the linear address into a physical address. Then processors perform the read or write operation on the specified memory location. When the page being accessed is not presently available in physical memory, the processor interrupts the execution of the program and generates a page-fault exception signal. After that, the operating system reads the page into physical memory from the disk and then executes the program. The swapping or exchange of pages between the physical memory and the disk must be transparent. The programs written for Intel Architecture 16-bit processors can be paged when these programs are executed in virtual 8086 mode. The concept of segmentation and paging in protected mode is already explained. In this section, paging of virtual 8086 mode had been discussed.

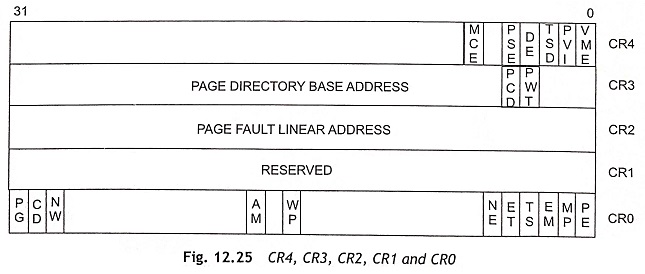

In virtual 8086 mode, control registers CR0 to CR4 control the paging unit. Figure 12.25 shows the control registers CR4, CR3, CR2, CR1 and CRO. The 31 bits of CR0 (PG) is used to turn paging ON (1) or OFF (0). When the paging is OFF, the linear address becomes the physical address. If paging is ON, the linear address must be converted into the physical address by the Paging Unit (PU). The Page Size Extensions (PSE) flag is bit-4 of CR4 and it is used to enable 4 Mbyte pages. If the PSE flag is clear, the common page length of 4 Kbytes is used. The page directory base address is stored in CR3. CR3 also holds the memory interface bits PCD and PWT. These bits are used to control the cache operation in IA-32 Pentium processor.

Page Tables and Directories

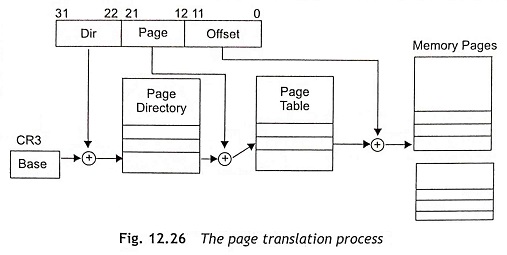

The linear address consists of the page directory entry, the page table entry and the page-offset address. Figure 12.26 shows the page-translation process from linear address to physical address in memory pages. The page directory has an array of 32-bit page-directory entries restricted in a 4 Kbyte page. The maximum 1024 page-directory entries can be held in a page directory.

Page table is an array of 32-bit page-table entries restricted in a 4 Kbyte page. About 1024 page-table entries can be held in a page table. The page tables cannot be used for 2 Mbyte or 4 Mbyte pages. The 2 Mbyte or 4 MByte page sizes are mapped directly from one or more page-directory entries.

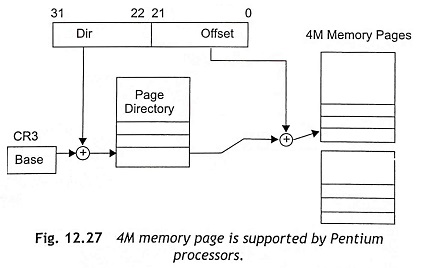

Usually the page directory is about 1K x 4 bytes or 4 Kbytes. Each page table is also 4 Kbytes. As there are 1024 (1K) possible page tables, a fully paged Pentium system requires 4 Mbytes + 4K to express the paging. But most of the operating systems do not use a fully paged memory system. Pentium processors support the 4M paging. When the Pentium processor supports 4M paging, there is no need of page tables and the page directory can be used to addresses a 4 Mbyte memory page. Figure 12.27 shows the 4M memory page supported by Pentium processors.

Translation Look-aside Buffers

It is clear from the paging system of Pentium processor that two memory accesses are required before addressing the specified physical address. This is a huge bottleneck of a paging technique. To improve the paging system, IA-32 Pentium processors use a Translation Look-aside Buffer (TLB), which is a cache of recently used page translations. When a page-table entry is in the TLB, the paging unit uses the TLB to implement the paging system. If a page-table entry is not present in the TLB, it is required to read memory to get the page directory and page-table contents which are needed for the translation. Usually, TLBs are smaller than normal caches. The Pentium processors have separate TLBs for code cache and data cache.