What is Current Foldback?

The current limiting technique maintains a constant load current at some specified value and under overload condition, the Vout drops to zero. But, in case of short circuiting under overload conditions the maximum current flows into the regulator. To protect regulator from overload condition, current foldback method is employed.

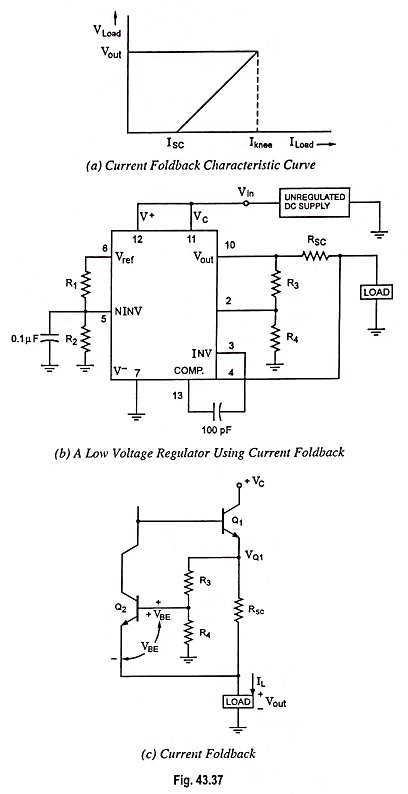

As shown in the current feedback characteristics [Fig. 43.37(a)], as current requirement increases, the output voltage is held constant till a fixed current level, Iknee is reached. If the current requirement reaches above this level, both output voltage and output current decrease. The circuit in Fig. 43.37(b) shows the requirement of current foldback.

The voltage at pin 3 is divided by R3-R4 network. Pin 3 is junction of base of Q2 and emitter of Q1 (or say V0). The current limit transistor Q2 conducts only when the drop across the resistance Rsc is large enough to produce a base-emitter voltage of Q2 to be at least VBE. When Q2 starts conduction, Q1 turns off and hence IL decreases. This results in decrease of volt drop at emitter of Q1, say VEQ1 and also the output voltage V0.

Thus, the voltage at pin 3 drops by smaller amount as compared to at pin 2. This increase in VBE of Q2 or increase in conduction of Q2 decreases conduction of Q1. Thus, IL again gets reduced. The process continues till Vout = 0 V and VEQ1 makes 0.5 V between pin 3 and pin 2. This is Isc and thus has been lowered by both IL and Vout.