What is Segmentation in Pentium Processor?

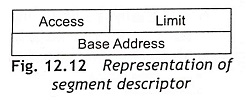

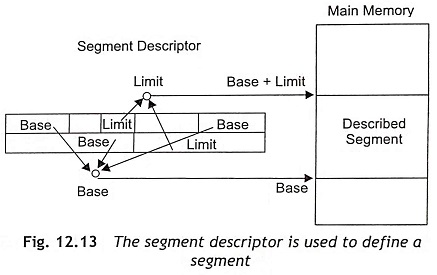

What is Segmentation in Pentium Processor? – When segmentation is used in memory management of the Pentium processor, the processor’s linear address space is broken up into a set of segments. Each segment must be specified by a segment descriptor, which defines the base address of the segment, the size or limit of the segment and its access rights. Figure 12.12 shows the simplified representation of the segment descriptor and Fig. 12.13 shows how the segment descriptor is used to define a segment.

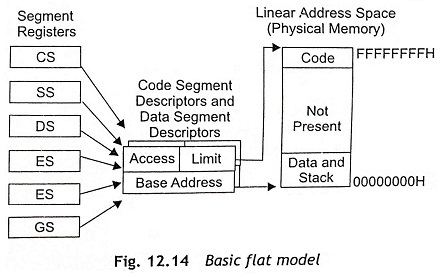

Using different settings of the segmentation registers, the processor’s linear address space can be organized into three different memory models such basic flat model, protected flat model, and multisegment model. Paging can be operated with any of the segmentation models. In this section, all three modes are discussed elaborately.

Basic Flat Model

The most simple memory model for a Pentium system is the basic flat model. In this system model, the operating system and application programs use a continuous, unsegmented address space. Usually, the basic flat model hides the segmentation mechanism from both the system designer as well as the application programmer. The segmentation cannot be disabled. To use the Segmentation in Pentium Processor, proper setting up of the segmentation registers is required. For implementation of basic flat memory model, at least two segment descriptors are required, one for a code segment and the other for a data segment. Subsequently, both code and data segments can be used to map the entire linear address spaces as shown in Fig. 12.14. The entire linear address spaces have the same base address value of 00000000H and the segment limit of FFFFFFFFH or 4 Gbytes.

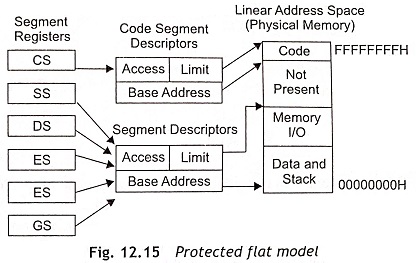

Protected Flat Model

Figure 12.15 shows the protected flat memory model for a system. The protected flat model is just like the basic flat model, except the segment limits are set to include only the range of addresses for which physical memory actually exists. The general-protection exception, G̅P̅ (#GP) is generated when any attempt has been taken to access non-existent memory. This model provides a minimum level of hardware protection against program bugs. If the protected flat model is combined with the paging mechanism, a higher level of protection can be achieved. Usually, Network Technology (NT) uses this technique to get a high level of protection.

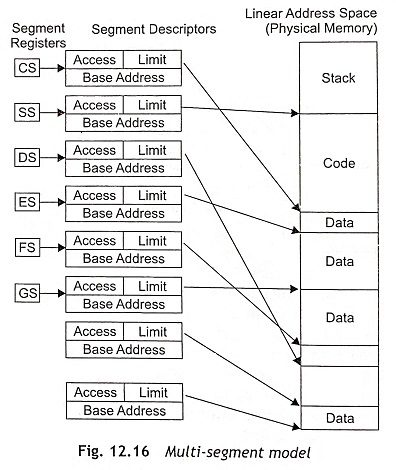

Multisegment Model

Figure 12.16 shows the multisegment memory model for a system. The multi-segment model has the segmentation capabilities to provide hardware-enforced protection of code, data structures, and programs and tasks. Each program (or task) should have its own table of segment descriptors and its own segments. The segments will be completely private to their corresponding assigned programs. Access to all segments of the system and the execution environments of all individual programs running on the system are hardware controlled.

The access check operations are used to protect against referencing an address outside the limit of a segment, and also against performing disallowed operations in certain segments. Usually, code segments are read-only segments. As a result, hardware can prevent writes into code segments. The access rights information can also be used to set up protection levels. Actually, the protection levels are used to protect operating-system procedures from any unauthorized access by application programs.